8 To 1 Multiplexer Verilog

2:1 4:1 8:1 Mux using structural verilog. GitHub Gist: instantly share code, notes, and snippets. /download-padlet-app-for-mac.html. Design and develop the Verilog /VHDL code for an 8:1 multiplexer. Simulate and verify its working.

8 To 1 Multiplexer Circuit Diagram

Introduction

An 8-to-1 multiplexer is a digital device that selects one of the eight inputs lines to the output line by using three-bit selection line. The block diagram of 8-to-1 Mux is shown in Figure 1. A 2n-to-1 multiplexer needs n bit selection line to select one of the 2n inputs to the output.Figure 1. Block diagram of 8-to-1 multiplexer Truth Table

Figure 2 shows the truth table of the 8-to-1 multiplexer. I1 to I8 are the input lines, S1 - S3 are the selection lines and O is the output line.Figure 2. Truth table of 8-to-1 multiplexer Verilog Module

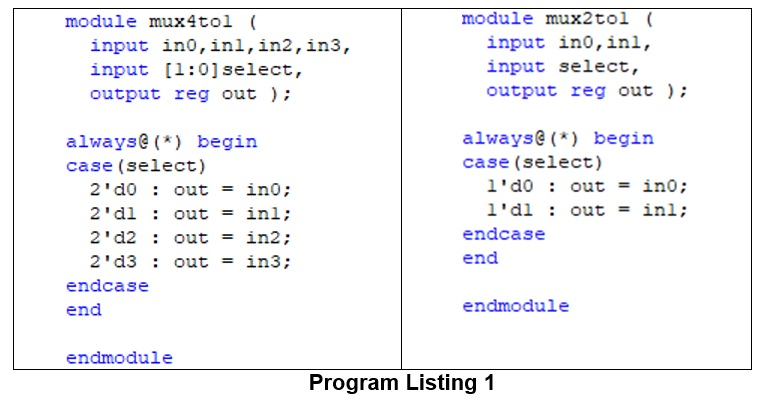

Figure 3 shows the Verilog module of the 8-to-1 multiplexer. The 8-bit ports In1 to In8 are input lines of the multiplexer. The Sel port is the 3-bit selection line which is required to select between the eight input lines. 8-bit port Out is the output line of the multiplexer.Figure 3. Verilog module of 8-to-1 multiplexer Verilog Code for the 8-to-1 Multiplexer (mux8to1.v)

Figure 4. Verilog Code for 8-to-1 multiplexer Verilog Test Bench for 8-to-1 Multiplexer (mux8to1_tb.v)

Figure 5. Verilog Test-Bench for 8-to-1 multiplexer Timing Diagram

Figure 6. Timing diagram of 8-to-1 multiplexer